# **DATASHEET**

# TMC453

# TRINAMIC MOTION CONTROL CHIP

TRINAMIC Motion Control GmbH & Co KG Sternstraße 67 20357 Hamburg GERMANY

T +49 - (0) 40 - 51 48 06 - 0 F +49 - (0) 40 - 51 48 06 - 60 WWW.TRINAMIC.COM INFO@TRINAMIC.COM

V2.3 / 1-Oct-04

### Life support policy

TRINAMIC Motion Control GmbH & Co KG does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Motion Control GmbH & Co KG.

Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.

#### © TRINAMIC Motion Control GmbH & Co KG 2004

Information given in this data sheet is believed to be accurate and reliable. However no responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result form its use.

Specifications subject to change without notice.

| Tab | <u>le of contents</u>                                                   |    |

|-----|-------------------------------------------------------------------------|----|

| 1   | Features                                                                | 4  |

| 2   | Introduction                                                            | 4  |

| 2   | .1 Control of Stepper Motors                                            | 4  |

| 2   | .2 Microstepping                                                        | 4  |

| 2   | .3 More precision using motor current control                           | 5  |

| 2   | .4 Conclusion                                                           | 5  |

| 3   | Block diagram                                                           | 6  |

| 4   | Electrical data of the TMC453                                           | 7  |

| 4   | .1 Pinout                                                               | 7  |

| 4   | .2 Absolute Maximum Ratings                                             | 8  |

| 4   | .3 Analog functions                                                     | 8  |

| 4   | .4 Digital part                                                         | 8  |

| 4   | .5 Characteristics of the analog components of the TMC453               | 9  |

| 5   | The Bus interface                                                       | 11 |

| 5   | .1 Parallel Interface                                                   | 11 |

| 5   | 2 Serial Interface                                                      |    |

| 6   | Description of the COMMAND FIFO                                         |    |

| 6   | .1 Accessing the TMC453                                                 | 14 |

| 6   | .2 General functionality                                                |    |

| 6   | .3 Description of the registers of the COMMAND FIFO                     | 14 |

|     | 6.3.1 FIFO Commands                                                     |    |

|     | 6.3.2 Description of the status bits                                    |    |

|     | 6.3.3 STOP and SLOWDOWN-functions                                       |    |

|     | 6.3.4 Finding the Reference Position                                    |    |

|     | 6.3.5 Programming example for the FIFO                                  |    |

| 7   | The Ramp Generator                                                      |    |

| 7   | .1 General Description                                                  |    |

|     | .2 Principle of Operation                                               |    |

| 7   | .3 Programming the Ramp generator                                       |    |

|     | 7.3.1 Automatic Ramp generation                                         |    |

|     | 7.3.2 Programmed / Interactive Ramp generation                          |    |

|     | 7.3.3 Synchronization of multiple TMC453s                               |    |

|     | 4 Ramp adaptive motor current control                                   |    |

| 8   | The Incremental Encoder Interface                                       |    |

|     | .1 General Description                                                  |    |

|     | .2 Registers of the Incremental Encoder Interface                       |    |

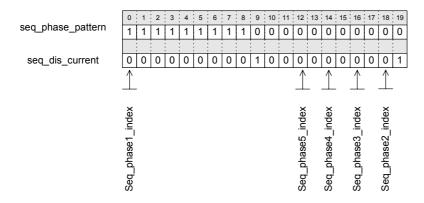

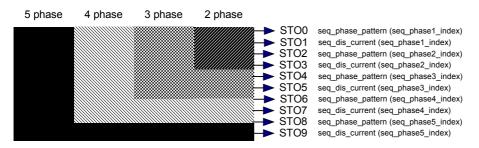

| 9   | The Sequencer                                                           |    |

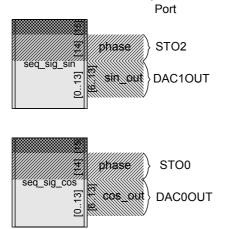

| 9   | .1 Registers for Sinestep operation                                     |    |

|     | 9.1.1 Programming the Sine Generator                                    |    |

| 9   | 2 Full- and Halfstep Operation                                          |    |

|     | 9.2.1 Automatic Phase Pattern Setup                                     |    |

| _   | 9.2.2 Manual Phase Pattern Setup                                        |    |

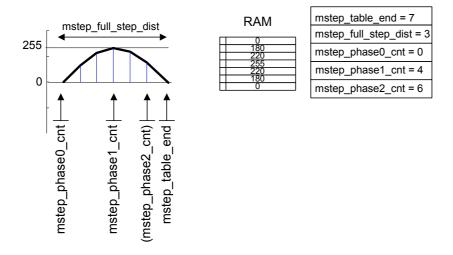

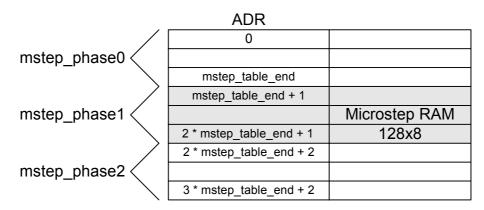

|     | Registers for Microstep Operation                                       |    |

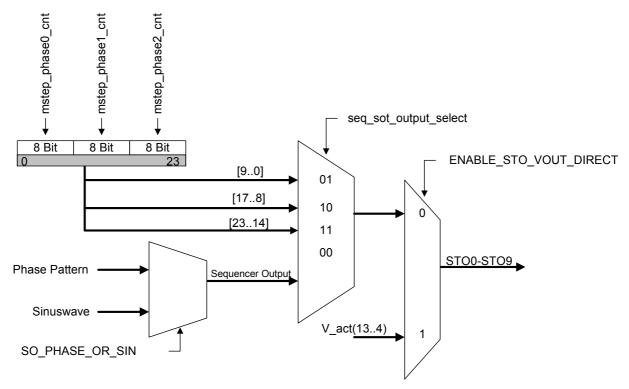

|     | 4 Administration of the different modes of operation and output control |    |

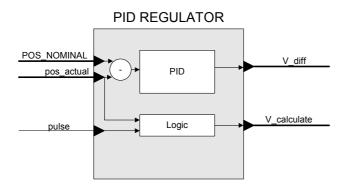

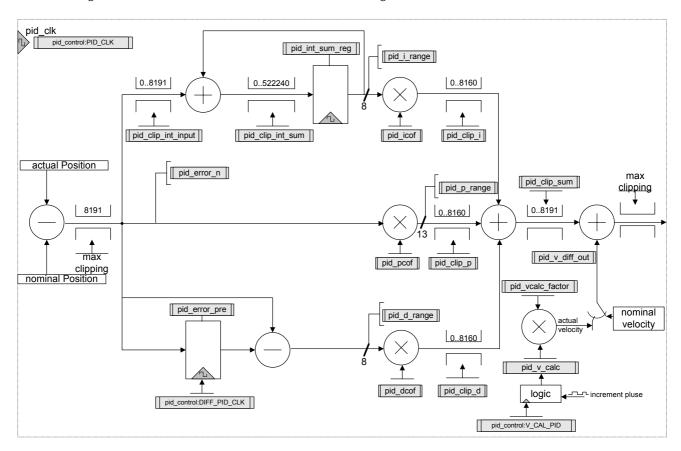

| 10  | The PID Controller                                                      |    |

| 1   | 0.1 General introduction                                                |    |

|     | 10.1.1 Increasing stepping accuracy and stabilizing the position        |    |

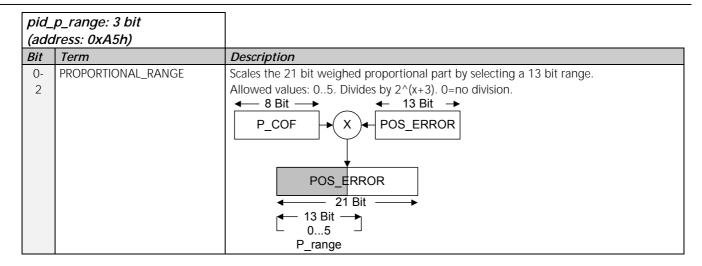

|     | 0.2 Description of the registers of the PID controller                  |    |

| 11  | Interrupt control and Interrupt Sources                                 |    |

| 12  | TMC453 Register Overview                                                | 48 |

#### 1 Features

#### **General Features**

- Seven stage command FIFO relieves host processor from all real-time requirements

- Step pulse generation from millihertz to megahertz

- Three 8 Bit DACs for direct microstep control of 2- and 3-phase stepper motors

- Optional pulse- and direction interface

- 8 Bit parallel interface / serial 2-wire interface

- Low Power 5V, 0.8µm CMOS process

- Direct interfacing to industry standard power drivers

- Package: PLCC68 (-PI) / CLCC68 (-CI) or dice (bare chip) (-D)

- Extended temperature range -25..+85°C

#### Ramp Generation

- Automatic generation of S-shaped ramps

- Synthesis of ramps of any shape with constant, linear and parabolic segments

- Synchronization between multiple TMC453s

- Programmable interrupt events

- Control inputs for stop and slowdown

#### Sequencer

- Freely programmable halfstep, fullstep and microstep patterns

- Supports 2-, 3-, 4- and 5-phase stepper motors with unipolar or bipolar control

- Sine generator for up to 256 microsteps per fullstep

- Intelligent motor current control

- 128X8 RAM for user defined microsteps adapted to the motor characteristics

- Direct output of the velocity value for servo motor control

#### Incremental Encoder

Supports 2-phase incremental encoders for position control and feedback control loop

#### Feedback controlled motion

- Stabilization against varying motor loads

- Exact position control via incremental encoder

#### 2 Introduction

#### 2.1 Control of Stepper Motors

Stepper motors are historically used in applications, where a positioning to preprogrammed or calculated positions is needed. Examples are linear and rotational axes in robots. The reason for using stepper motors in these applications is that they work extremely precise without the necessity to use a control loop. Precautions have to be taken to avoid overloading the motor, e.g. by too fast movements or too high accelerations. In many of these applications an incremental encoder is coupled mechanically to the motor to measure the position or velocity or to detect failures.

New applications for stepper motors have the demand for a high reliability while reducing costs, e.g. the minimization of mechanical parts, which is possible because the stepper motor provides high torque without gear and precise positioning without feedback. It is expected that stepper motors and electronically commutated motors will replace DC motors in many applications which incorporate DC motors today. The reduction in cost is possible because control electronics continues to get less expensive while costs of mechanic parts cannot be reduced in such a dramatic way.

The TMC453 is a universal controller for stepper motors. It interfaces directly to a CPU and offloads the CPU from all time critical tasks.

After setting up the chip with a number of control parameters, the motor can be controlled by simply programming the target position for a movement. The TMC453 automatically drives the motor with smooth movement curves (ramps) to reduce mechanical stress and to avoid the loss of steps. Where necessary the CPU can control all phases of the movement itself.

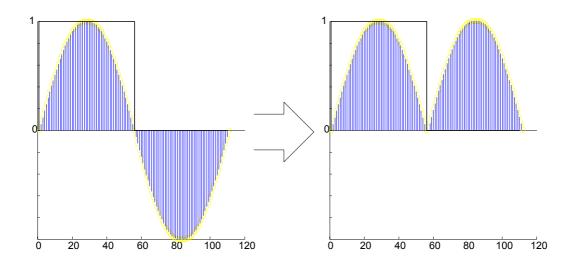

#### 2.2 Microstepping

A stepper motor has an inherent resolution given by the number of fullsteps per rotation. These positions are achieved by switching the coils on and off. In applications where a higher step resolution than the inherent step

resolution or its double, the halfstep resolution, is required, a control scheme called microstepping can be used. It allows a positioning of the motor between the full (or half) steps. Therefore the coils of the motor are driven by weighed currents. In principle, a sine-wave driving scheme would be sufficient, but since the characteristics of most motors are not linear, it is desirable to be able to program the current patterns for a number of microsteps between each two fullsteps. Using microstepping can also be necessary to reduce the abruptness of the change between two full-/halfstep positions.

A stepper motor is very sensitive to static and changing loads in microstep positions. In cases where microstepping is used to improve the accuracy of positioning, a feedback control system using a position encoder reduces the need for adjustment of the microstepping table and minimizes the effect of varying loads. The TMC453 contains a programmable filter to build a PID-(Proportional-Integral-Differential) regulator for position stabilization.

## 2.3 More precision using motor current control

In most of today's applications based on stepper motors, the motors are driven with the full current, independent of the torque actually needed. This not only wastes energy, reduces lifetime of electronical and mechanical parts, but also reduces precision because of the thermal expansion of the mechanical parts.

Since the torque of a stepper motor is a function of the coil current, the required current depends on load and acceleration. The TMC453 supports an effective means to reduce power consumption: It monitors acceleration and speed to adjust the motor current according to a user defined table. TMC453 users have reported a dramatic reduction of thermal problems.

#### 2.4 Conclusion

The TMC453 is an efficient and inexpensive motor controller. It integrates the complete control function set to drive all kinds of stepper motors and directly interfaces to power drivers. Further on it integrates interfaces and the logic to control DC servo motors. Programming of the TMC453 is easy, because it integrates all time critical features in hardware. Only a few parameters have to be programmed to adapt the TMC453 to a given application. Then the TMC453 does all the positioning by just programming the desired target position and motor velocity. The TMC453 provides the ultimate function set to get the highest possible resolution without the necessity for feedback while also integrating the complete logic for feedback control without processor overhead.

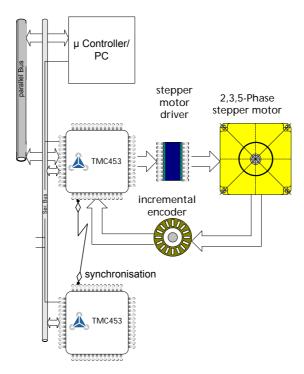

Figure 2-1: System environment of the TMC453

Depending on the requirements the TMC453 can be programmed via a serial or a parallel interface. It provides an efficient synchronization mechanism to control multiple motors synchronously.

This large set of features is controlled via 84 integrated registers. While this may seem to be a large number of function, control and status registers, only 4 registers have to be programmed to start an automatic ramp function.

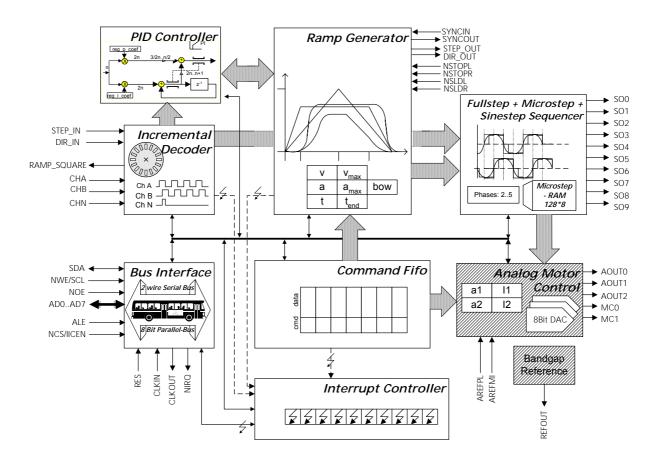

## 3 Block diagram

The TMC453 is built in a modular way. Every module realizes a defined set of functions. Only the modules which are needed for an application have to be programmed.

Figure 3-1: Block diagram of the TMC453's modules

# 4 Electrical data of the TMC453

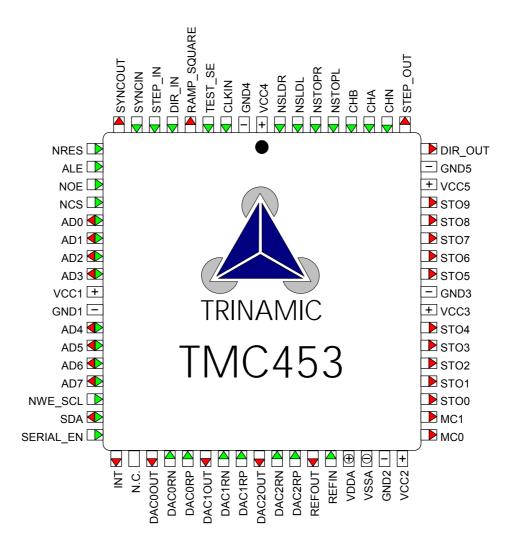

## 4.1 Pinout

Pin 1 is marked by a dot on the package and is in the middle of the flattened side.

| Pin               | PLCC68        | In/Out  | Description                                                                               |

|-------------------|---------------|---------|-------------------------------------------------------------------------------------------|

| NRES              | 10            | 1       | Reset (inverted)                                                                          |

| ALE               | 11            | i       | Address Latch Enable (1=Address valid)                                                    |

| NOE               | 12            | i       | Output Enable (inverted)                                                                  |

| NCS               | 13            | i       | Chip Select (inverted)                                                                    |

| AD0-AD7           | 14-17, 20-23  | I/O     | Bidirectional Address-/Data bus                                                           |

| NWE_SCL           | 24            | I       | Write Enable (inverted) / Serial Clock                                                    |

| SDA               | 25            | I/O     | Serial Data (O.C.)                                                                        |

| SERIAL_EN         | 26            | I       | Serial Enable (reset-option)                                                              |

| INT               | 27            | 0       | Interrupt Output (polarity programmable)                                                  |

| DAC0OUT           | 29            | 0       | Output of DAC 0                                                                           |

| DACORN            | 30            | ı       | Negative reference input of DAC0                                                          |

| DACORP            | 31            | 1       | Positive reference input of DACO                                                          |

| DAC1OUT           | 32            | 0       | Output of DAC 1                                                                           |

| DAC1RN            | 33            | ı       | Negative reference input of DAC1                                                          |

| DAC1RP            | 34            | 1       | Positive reference input of DAC1                                                          |

| DAC1RF<br>DAC2OUT | 35            | 0       | Output of DAC 2                                                                           |

|                   | 36            | ı       | Negative reference input of DAC2                                                          |

| DAC2RN<br>DAC2RP  | 37            | 1       |                                                                                           |

| -                 |               | 0       | Positive reference input of DAC2                                                          |

| REFOUT            | 38            | 0       | Output of Reference Voltage Source                                                        |

| REFIN             | 39            | 0 (0 1) | Input of Reference Voltage Amplifier                                                      |

| MC0,MC1           | 44,45         | O (8mA) | Digital Control of Motor Current                                                          |

| STO0-STO9         | 46-50, 53-57  | O (8mA) | Digital Motor Control Outputs for full-/half step patterns sine waves and velocity values |

| DIR_OUT           | 60            | O (8mA) | Direction Output                                                                          |

| STEP_OUT          | 61            | O (8mA) | Step Impulse Output (1 clock high on change of position)                                  |

| CHN               | 62            | I (S)   | Null-Signal of Incremental Encoder                                                        |

| СНА               | 63            | I (S)   | Channel A of Incremental Encoder                                                          |

| СНВ               | 64            | I (S)   | Channel B of Incremental Encoder                                                          |

| NSTOPL            | 65            | I (S)   | End Switch Left                                                                           |

| NSTOPR            | 66            | I (S)   | End Switch Right                                                                          |

| NSLDL             | 67            | I (S)   | Slowdown Switch Left                                                                      |

| NSLDR             | 68            | I (S)   | Slowdown Switch Right                                                                     |

| CLKIN             | 3             | 1       | System Clock                                                                              |

| TEST_SE           | 4             | 1       | Test Enable (activates scan test, switches analog part off)                               |

|                   |               |         | Tie this input to GND for operation!                                                      |

| RAMP_             | 5             | O (8mA) | Symmetrical Step Impulse Output                                                           |

| SQUARE            |               |         |                                                                                           |

| DIR_IN            | 6             | 1       | External Step Input: Direction                                                            |

| STEP_IN           | 7             | 1       | External Step Input: Pulse (edge triggered, min. pulse length 1 clock)                    |

| SYNCIN            | 8             | 1       | Synchronization Input for Command FIFO                                                    |

| SYNCOUT           | 9             | 0       | Synchronization Output for Command FIFO                                                   |

| VCC               | 1,18,43,51,58 |         | Digital Supply 5V                                                                         |

| GND               | 2,19,42,52,59 |         | Digital Ground                                                                            |

| VDDA              | 40            |         | Analog Supply 5V                                                                          |

| VSSA              | 41            |         | Analog Ground                                                                             |

| (C) C-l!          |               | l .     | 1                                                                                         |

<sup>(</sup>S) are Schmitt-Trigger inputs

#### 4.2 Absolute Maximum Ratings

DC Supply Voltage  $-0.3V \le VDD \le 7V$

DC Voltage on any Pin VSS -0.3V≤ Vin ≤VDD+0.3V

$\begin{array}{lll} \mbox{Input Current} & \leq 10\mbox{mA} \\ \mbox{Output Current} & \leq 50\mbox{mA} \\ \mbox{ESD Voltage on any Pin} & 1000\mbox{V} \\ \mbox{Max. Junction Temperature} & \leq 150\mbox{°C} \\ \mbox{Storage Temperature} & -65\mbox{°C} \leq 150\mbox{°C} \\ \end{array}$

#### Recommended Operating Conditions / Typical Characteristics

|                            | Min | Тур | Max | Units |

|----------------------------|-----|-----|-----|-------|

| Digital Supply Voltage VCC | 4.5 | 5.0 | 5.5 | V     |

| Analog Supply Voltage VDD  | 4.5 | VCC | 5.5 | V     |

| Tamb                       | -25 | +25 | +85 | °C    |

| Operating Frequency        | 0   | 12  | 16  | MHz   |

| Supply Current             |     | 3   |     | mA    |

| f=0 MHz                    |     |     |     |       |

| Supply Current             |     | 25  |     | mA    |

| f=10MHz                    |     |     |     |       |

## 4.3 Analog functions

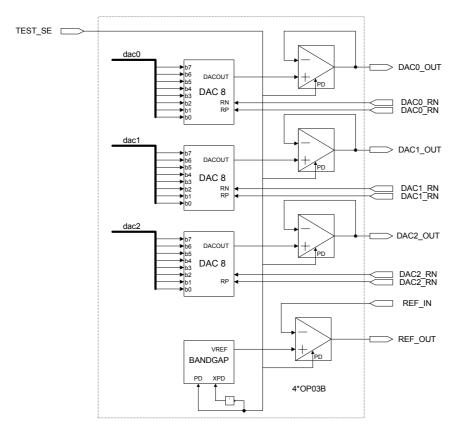

The TMC453 contains an analog part integrating three DACs buffered by operational amplifiers and a reference voltage source which can be programmed via an external resistive divider. The reference inputs of all DACs are accessible separately. This allows different functions to be realized, for example current control for a two phase motor, by supplying the reference inputs of DAC 0 and DAC 1 with the output voltage of DAC 2.

## 4.4 Digital part

TTL DC Characteristics (VDD 5V ± 10 %; -25°C ≤TA ≤ 85°C)

|                                | Min | Тур | Max | Units |

|--------------------------------|-----|-----|-----|-------|

|                                |     |     |     |       |

| Input Low Level                | 0   |     | 0.8 | V     |

| Input High Level               | 2.0 |     | 5.5 | V     |

| Switching Threshold            |     | 1.5 |     | V     |

| Schmitt Trigger Neg. Threshold | 1.2 |     | 1.8 | V     |

| <i>VDD=5.0V</i>                |     |     |     |       |

| Schmitt Trigger Pos. Threshold | 3.0 |     | 3.7 | V     |

| <i>VDD=5.0V</i>                |     |     |     |       |

| Schmitt-Trigger Hysteresis     |     | 1.8 |     | V     |

| Output Low Level, I=4mA        |     |     | 0.4 | V     |

| (resp. I=8 mA)                 |     |     |     |       |

| Output High Level, I=-4mA      | 4.0 |     |     | V     |

| (resp. I=-8 mA)                |     |     |     |       |

| Input Current                  |     | ± 1 |     | μΑ    |

| High Impedance Current         |     |     | 10  | μΑ    |

| (GND to VDD)                   |     |     |     |       |

| Output Short Circuit Current   |     |     | 50  | mA    |

| <i>VDD =5.5V</i>               |     |     |     |       |

| Input Capacitance              |     | 2   |     | pF    |

| Output Capacitance             |     | 5   |     | pF    |

# 4.5 Characteristics of the analog components of the TMC453

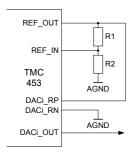

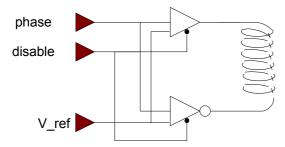

Figure 4-1: Analog components of the TMC453.

| OP AMP                             | Min | Тур  | Max     | Units |

|------------------------------------|-----|------|---------|-------|

| Offset                             | -10 |      | +10     | mV    |

| Amplification                      |     | 113  |         | dB    |

| Bandwidth                          |     | 1.4  |         | MHz   |

| Slew rate                          |     | 2.7  |         | V/µs  |

| Current consumption                |     | 0.63 |         | mA    |

| Input voltage range                | 0.2 | -    | Vdd-0.7 | V     |

| Output voltage range<br>RI=2.2kOhm | 0.2 |      | Vdd-0.7 | V     |

| Bandgap Reference                  | Min  | Тур  | Max  | Units |

|------------------------------------|------|------|------|-------|

| Output Voltage<br>(REFIN = REFOUT) | 1.12 | 1.25 | 1.38 | V     |

| Current Consumption                |      | 100  |      | μΑ    |

| Output Voltage Range               | 1.25 |      | 4.3  | V     |

| DAC 8                        | Min                    | Тур    | Max  | Units |

|------------------------------|------------------------|--------|------|-------|

|                              |                        |        |      |       |

| Differential nonlinearity    |                        | ± 0.25 |      | LSB   |

| Integral nonlinearity        |                        | ± 0.5  |      | LSB   |

| Offset Voltage               |                        | ± 0.25 |      | LSB   |

| Reference Impedance          | 6.7                    | 8      | 10.4 | kΩ    |

| Power Supply Range           | 4.5                    | 5      | 5.5  | V     |

| Vrefp-Vrefn =1V              |                        |        |      |       |

| Power Supply Vrefp-Vrefn =1V |                        | 0.15   |      | mA    |

| Power Consumption            |                        | 0.65   |      | mW    |

| Output Resistance            | , in the second second | 21     |      | kΩ    |

| Settling Time                |                        |        | 1    | μs    |

DACOUT = (VRP-VRN)/256 \* dac\_data + VRN

| Typical performance of analog | Min  | Тур   | Max     | Units |

|-------------------------------|------|-------|---------|-------|

| outputs in sample application |      |       |         |       |

| Output voltage range Vout     | 0.25 |       | Vdd-0.7 | V     |

| Integral nonlinearity         |      | ± 0.5 |         | LSB   |

| Offset Voltage                |      | ± 20  |         | mV    |

| Reference Impedance           | 6.7  | 8     | 10.4    | kΩ    |

Vout = (VRP-VRN)/256 \* dac\_data + VRN

#### Hints for the design of the supply:

The pins VSSA and GND should be connected directly near the case of the TMC453. The analog supply voltage and the digital supply voltage should not deviate more than about 1V in operation.

#### Note on the usage of the reference voltage source:

Use a voltage divider with a total resistance of typical 10 to  $100k\Omega$  to set the voltage at the reference output. Vout = Vref \* (R1+R2) / R2

#### Note on the usage of the analog outputs:

The output voltage range of the TMC453 is limited by the integrated operational amplifiers to about 0.2V to 4.3V. When the (lower) offset voltage range in an application is critical, e.g. for precise micro step applications, the reference voltage should be chosen as high as possible (ca. 3 - 4.3V), to minimize this effect. To remove the offset voltage completely, the lower reference of the DACs can be raised to 0.2 - 1V. This voltage then has to be used as lower reference for the motor drivers or can be externally subtracted from the output voltage, for example using an operational amplifier as analog adder.

The integrated operational amplifiers are not suitable for driving long cables. Large capacitive loads should be isolated using a series resistor.

#### 5 The Bus interface

The TMC453 has got both a parallel interface with multiplexed address/data bus and a serial 2-wire interface to allow communication with a host processor. The parallel interface can either be directly connected to a host processor or can be driven via port lines. The serial interface also allows operation of other circuits on the same bus. Which interface is enabled is decided by the polarity of the SERIAL\_EN pin during a chip reset. The polarity of SERIAL\_EN is latched with the rising edge at the /RES pin.

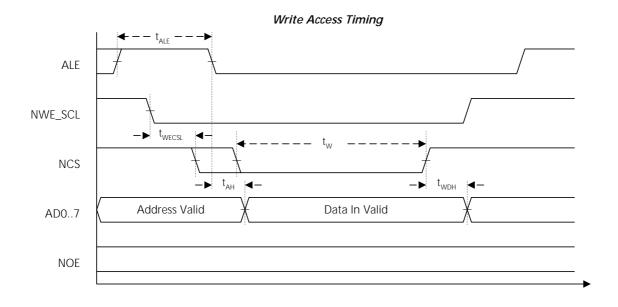

#### 5.1 Parallel Interface

The parallel interface allows direct connection to processor systems with multiplexed address/data bus like the 8051 series. It is important to make sure that the TMC453 is clocked fast enough to satisfy the access time requirements of the processor. For non-multiplexed processor systems it is possible to decode the TMC453s ALE signal on one address of the CPUs address space and the TMC453s /CS on the following address. This allows write accesses to the TMC453 using two subsequent writes and read accesses using a write access to the address register and a subsequent read access to the data register. Another possibility is control of the TMC453 using 11 I/O ports. This is especially recommended when many TMC453s are controlled by one processor or the distance between host CPU and TMC453 is large.

Figure 5-1: Timing of the parallel interface

| Symbol                       | Meaning                                                 | Min                        | Max                       |

|------------------------------|---------------------------------------------------------|----------------------------|---------------------------|

| $t_{\scriptscriptstyle ALE}$ | ALE active time                                         | 30 ns                      | -                         |

| t <sub>wecsl</sub>           | Write enable valid to CS active or ALE inactive         | 10 ns                      | -                         |

|                              | (whichever comes last)                                  |                            |                           |

| $t_{AH}$                     | Address hold time after ALE inactive                    | 10 ns                      | -                         |

| $t_w$                        | Write time. A write occurs during the overlap of an     | 1 t <sub>clk</sub> + 10 ns | -                         |

|                              | active CS, active WE and inactive ALE.                  |                            |                           |

| $t_{\scriptscriptstyle WDH}$ | Write data hold time after Write end                    | 10 ns                      | -                         |

| t <sub>wrec</sub>            | Write recovery time. Time from write access end to next | 2 t <sub>clk</sub>         | -                         |

|                              | Write / Read access                                     |                            |                           |

| $t_{_{RDV}}$                 | Read access time. Time from read start to valid data    | -                          | 3 t <sub>clk</sub> +20 ns |

|                              | out. A read occurs during the overlap of an active CS,  |                            |                           |

|                              | inactive WE and inactive ALE.                           |                            |                           |

| t <sub>rrec</sub>            | Read recovery time. Time from read access end to next   | 1 t <sub>clk</sub>         | -                         |

|                              | write / read access                                     |                            |                           |

| $t_{_{RHZ}}$                 | Output tristate time (from CS, WE, OE or ALE)           | 0 ns                       | 10 ns                     |

1)  $t_{\rm clk}$  is the length of one clock period at the clock input of the TMC453,  $t_{\rm clk}$  = 80 ns (t.b.d.)

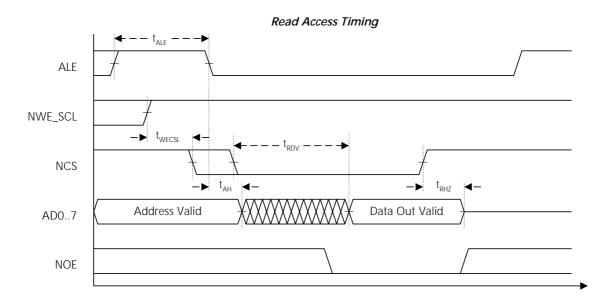

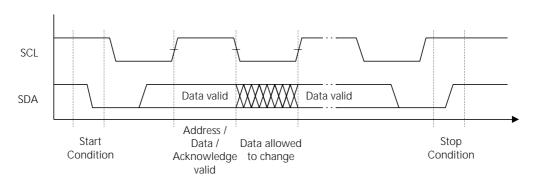

#### 5.2 Serial Interface

The serial 2-wire bus allows data transfer rates of several 100kbit/s and addressing of up to 128 TMC453s using a simple protocol. It uses the lines SDA and SCL (pin NWE\_SCL). The protocol can be simply implemented in software while hardware interfaces are available also. In this mode the address/data pins AD1 to AD7 select the serial address of the TMC453. The remaining pins of the parallel interface are not used and should be connected to a defined voltage (/CS inactive). The serial lines SCL and SDA are internally filtered over three system clocks.

The internal address counter is incremented after every access.

| Symbol                       | Meaning                                | Min                | Max |

|------------------------------|----------------------------------------|--------------------|-----|

| t <sub>scl</sub>             | SCL high / low time                    | 5 t <sub>clk</sub> | -   |

| $t_{suss}$                   | Start / Stop condition data setup time | 5 t <sub>clk</sub> | -   |

| $t_{\scriptscriptstyle HSS}$ | Start / Stop condition data hold time  | 5 t <sub>clk</sub> | -   |

1)  $t_{\mbox{\tiny clk}}$  is the length of one clock period at the clock input of the TMC453

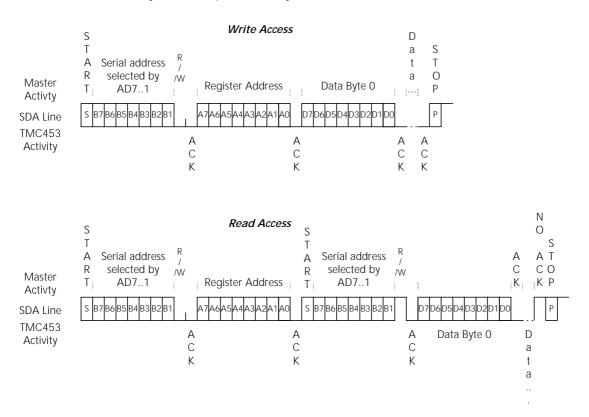

#### Serial Bus Data Transfer Sequence

Figure 5-2: Data transfer on the serial bus

The data line SDA is a bi-directional open-drain port. An external pullup resistor with a value of some kilo ohms is required for operation. During data transmission the logic level on SDA is only allowed to changed, when the level on SCL is low. Changes during the high-phase of SCL are reserved for start and stop conditions.

The clock line SCL is only used as input for the synchronization of the data bits.

Figure 5-3: Telegram on the serial bus

# 6 Description of the COMMAND FIFO

## 6.1 Accessing the TMC453

The TMC453 contains a set of registers with a width of up to 32 bits. Its bus interfaces transfer data in portions of 8 bits. To allow the access to 32 bit values, the TMC453 internally uses a 32 bit bus architecture. When accessing registers, which are wider than one byte, the new value is transferred into the internal register whenever the most significant byte is written. Therefore, the host processor has to write the bytes in ascending order, e.g. the least significant byte (lowest address) first. When using the serial bus interface this is already implied by the automatic address increment. Accordingly, when reading registers with a width of more than one byte, the least significant byte has to be read first. Whenever the first byte of a register is read, the complete register is copied into an internal latch, which is read on the subsequent accesses to the higher bits of the register. Thus it is guaranteed that the values are consistent.

#### Reset Values

All registers contain "all bits cleared" after reset, unless stated differently. All functions which can be enabled by register bits are enabled by a "one-" bit.

## 6.2 General functionality

This module controls all real time-critical functions in the TMC453. These are especially the functions for the generation of velocity ramps, as well as the control of motor parameters, which could have to be altered in different segments of a ramp. The system's microprocessor writes commands into the command FIFO which are executed sequentially whenever the preceding command is finished. The commands consist each of a number of actions and a condition for the termination. When the condition is met, the TMC453 continues with the execution of the next command at once. In fact the execution time is only three clock cycles, so that typically a number of values can be changed between each two motor steps.

## 6.3 Description of the registers of the COMMAND FIFO

| _     | mmand: 32 Bit<br>s: 0x00h) |                                               |

|-------|----------------------------|-----------------------------------------------|

| Bit   | Term                       | description                                   |

| 031 W | FIFO_COMMAND               | Entry of new commands into the FIFO           |

| 031 R | ACTIVE_COMMAND             | Readout of the command currently in execution |

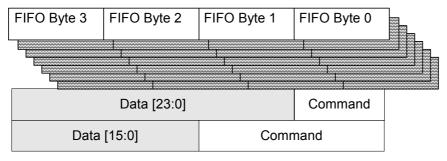

#### 6.3.1 FIFO Commands

The Command FIFO interprets a 32 bit wide command word in each execution step. The command can either consist of a 16 bit wide operation code and up to 16 data bits, or of an 8 bit wide operation code and up to 24 data bits. 24 data bits are used for position registers and time limit. The code in byte 0 of the command determines the type (width of the argument and opcode). Commands can only write to registers. Reading registers is possible via separate read-registers.

Figure 6-1: FIFO-Command types

### Structure of the two command types

| Command Type | FIFO Byte 3 (Bit 3124) | FIFO Byte 2 (Bit 2316) | FIFO Byte 1 (Bit 158)  | FIFO Byte 0 (Bit 70) |

|--------------|------------------------|------------------------|------------------------|----------------------|

| 24 Bit value | Value3 [2316]          | Value3 [158]           | Value3 [70]            | Control [70]         |

| 16 Bit value | Value2 [158]           | Value2 [70]            | Extended Control [158] | Control [70]         |

The parameters associated with Value2 / Value3 are adjusted with the LSB at the least significant bit position. It is always necessary to write the complete 32 bit entry, the most significant byte as last value.

## Components of the Command code, lower byte

| Contr | rol [07]       |                                                                                                                                                                                                                                                                               |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Term           | Description                                                                                                                                                                                                                                                                   |

| 03    | Command Opcode | Operation code (s. table)                                                                                                                                                                                                                                                     |

| 4     | WAIT_ON_SYNC   | When set: This command is not executed before SYNC_IN has got the polarity which is defined by Bit 5 (SYNC_POLARITY)                                                                                                                                                          |

| 5     | SYNC_POLARITY  | Polarity of SYNC_IN for the WAIT_ON_SYNC function                                                                                                                                                                                                                             |

| 6     | COPY_REG_INT   | When this flag is set, the following actions are done, when execution of the command is started:  1. The actual values of the ramp registers are copied to a set of holding registers  2. A FIFO-Interrupt is generated                                                       |

| 7     | FIFO_OVERRIDE  | When this bit is set in a command, all previous FIFO entries which write values are executed at once, while all ramp commands are skipped and the waiting conditions are ignored. Then the new command is executed.  This bit is interpreted at once when writing to the FIFO |

### Command Opcodes for bits 0..3

| Command  | Opcode | Description                                                    |                                                         |

|----------|--------|----------------------------------------------------------------|---------------------------------------------------------|

| PRP      | 0000   | Start parabolic ramp:                                          |                                                         |

|          |        | ,                                                              | ACT_ACCEL is increased continuously by the value        |

|          |        |                                                                | is increased continuously by the resulting acceleration |

|          |        | value.                                                         |                                                         |

|          |        | Necessary precondition: FIFO_BOW, FIFO_A_N                     |                                                         |

|          |        | Termination conditions: FIFO_A_NOM reache   FIFO_T_LIM reached | d, FIFO_V_NOM reached, FIFO_POS_END reached or          |

| LRP      | 0001   | Start linear ramp:                                             |                                                         |

|          |        | •                                                              | is added continuously to the velocity ACTVEL.           |

|          |        | Necessary precondition: ACT_ACCEL and FIFC                     | , , , , , , , , , , , , , , , , , , ,                   |

|          |        | Termination conditions: FIFO_V_NOM reached                     | d, FIFO_POS_END reached or FIFO_T_LIM reached           |

| CRP      | 0010   | Constant ramp (constant velocity):                             |                                                         |

|          |        | The velocity is not changed.                                   |                                                         |

|          |        | <b>Necessary preconditions:</b> The desired velocity           |                                                         |

|          |        | <b>Termination conditions:</b> FIFO_POS_END reach              | ned or FIFO_T_LIM reached                               |

| ARP      | 0011   | Start automatic ramp:                                          |                                                         |

|          |        | The motor is driven to its target position using               |                                                         |

|          |        | Necessary preconditions: ACTVEL=0; FIFO_BC                     | . – – – – – – – – – – – – – – – – – – –                 |

|          |        | Termination conditions: FIFO_POS_END reach                     | ·                                                       |

|          |        | ACTVEL=0 before starting an automatic ramp                     | ctive before, you should set the mode CRP and set       |

| SET_ANA  | 1000   | Setting analog registers:                                      | J.                                                      |

| JET_ANA  | 1000   | The register is specified by the Extended Conf                 | trol-ANA command code.                                  |

| SET_RMP  | 1010   | Setting parameters of the ramp generate                        |                                                         |

|          |        | The register is specified by the Extended Con-                 |                                                         |

| SET_TLIM | 1100   | Setting a time limit:                                          | (8 bit command with 24 bit parameters)                  |

|          |        | FIFO_T_LIM = Value3                                            |                                                         |

|          |        | The time limit register is loaded with the spec                | rified value.                                           |

| SET_POS_ | 1101   | Setting the position counter:                                  | (8 bit command with 24 bit parameters)                  |

| ACT      |        | POS_ACT = Value3                                               |                                                         |

|          |        | POS_ACT is loaded with the new value                           |                                                         |

| SET_POS_ | 1110 | Setting the target position:                                                                 | (8 bit command with 24 bit parameters) |

|----------|------|----------------------------------------------------------------------------------------------|----------------------------------------|

| END      |      | POS_END = Value3                                                                             |                                        |

|          |      | POS_END is loaded with the new value.                                                        |                                        |

| NOP      | 1111 | No operation resp. no change of the ramp mode:                                               |                                        |

|          |      | This opcode does not change the operation mode. The other command bits are evaluated as in a |                                        |

|          |      | 16 bit wide opcode.                                                                          |                                        |

# Structure of the Command code, upper byte, only with 16 bit command code, except with SET\_ANA command

With 8 bit command code the previous settings of the bits 12..15 are maintained.

| Exten | ded Control [815]      |                            |                |                                                           |

|-------|------------------------|----------------------------|----------------|-----------------------------------------------------------|

| Bit   | Term                   | Description                |                |                                                           |

| 811   | Register Write Command | The parameters selected    | with these b   | oits are loaded with the value which is given as Value2:  |

|       | Code                   | 0000: FIFO_A_NOM           | = Value2       | (14 Bit signed)                                           |

|       |                        | 0001: FIFO_V_NOM           | = Value2       | (14 Bit signed)                                           |

|       |                        | 0010: ACTACCEL             | = Value2       | (14 Bit signed)                                           |

|       |                        | 0011: ACTVEL               | = Value2       | (14 Bit signed)                                           |

|       |                        | 0100: FIFO_A_SLD           | = Value2       | (13 Bit unsigned)                                         |

|       |                        | 0101: FIFO_V_SLD           | = Value2       | (13 Bit unsigned)                                         |

|       |                        | 0110: FIFO_BOW             | = Value2       | (14 Bit signed)                                           |

|       |                        | 0111: FIFO_PRE_DIV4        | = Value2       | (4 Bit)                                                   |

|       |                        | 1110: FIFO_MISC_CTRL       | = Value2       | (2 Bit) (see Ramp Generator description)                  |

|       |                        | 1111: Do not change an     | y parameters   | S                                                         |

|       |                        | The values have to be rig  | ght adjusted   | with the width given in parentheses.                      |

| 12    | END_BY_POS             | Only when this flag is se  | t, the curren  | t command can be terminated by reaching the target        |

|       |                        | position. When cleared,    | this terminat  | ion condition is switched off. This flag has no influence |

|       |                        | on the automatic ramp.     |                |                                                           |

| 13    | END_BY_TIME            | Only when this flag is se  | t, the curren  | t command can be terminated when the time limit is        |

|       |                        | reached.                   |                |                                                           |

| 14    | SYNC_OUT_VAL           | This bit controls the pola | rity of the sy | nchronization output.                                     |

| 15    | CLEAR_TIMER            | When this bit is set, the  | time counter   | is set to zero upon command begin.                        |

### Structure of the command code, upper byte, only with SET\_ANA command

| Exten | ded Control [815]                      |                                                                                                                                                                                 |                                                                                                          |                                                                                                                                                                                                                                |

|-------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Term                                   | Description                                                                                                                                                                     |                                                                                                          |                                                                                                                                                                                                                                |

| 811   | SET_ANA Register Write<br>Command Code | The parameters of the anawhich is given as Value2: 0000: FIFO_A_COMP1 0001: FIFO_V_COMP1 0010: FIFO_A_COMP2 0011: FIFO_IMOTO 0101: FIFO_IMOT1 0110: FIFO_IMOT2 0111: FIFO_IMOT3 | = Value2<br>= Value2<br>= Value2<br>= Value2<br>= Value2<br>= Value2<br>= Value2<br>= Value2<br>= Value2 | elected by these bits are loaded with the value  (13 Bit unsigned) (13 Bit unsigned) (13 Bit unsigned) (13 Bit unsigned) (8 Bit unsigned) |

## 6.3.2 Description of the status bits

|     | status: 14 bit r<br>Iress: 0x04h) |                                                   |

|-----|-----------------------------------|---------------------------------------------------|

| Bit | Term                              | Description                                       |

| 02  | FIFO_ENTRIES                      | actual number of FIFO entries (07), 0=FIFO empty  |

| 8   | A_NOM_REACHED                     | nominal acceleration reached                      |

| 9   | V_NOM_REACHED                     | nominal velocity reached                          |

| 10  | POS_END_REACHED                   | target position reached                           |

| 11  | AUTO_ACTIVE                       | automatic ramp active                             |

| 12  | STOP_CONDITION                    | Stop condition has occurred                       |

|     |                                   | (Flag is cleared upon read of this register)      |

| 13  | SLD_CONDITION                     | Slowdown function is active (caused by a SLD pin) |

|     |                                   | (Flag is cleared upon read of this register)      |

| fifo_input_status: 5 Bit r |               |                                          |

|----------------------------|---------------|------------------------------------------|

| (add                       | lress: 0x06h) |                                          |

| Bit                        | Term          | Description                              |

| 0                          | SLD_RIGHT     | right slowdown switch is active          |

| 1                          | SLD_LEFT      | left slowdown switch is active           |

| 2                          | STOP_RIGHT    | right brake switch is active             |

| 3                          | STOP_LEFT     | left brake switch is active              |

| 4                          | SYNC_IN       | polarity of external synchronization pin |

| fifo_port_func: 2 Bit r/w |               |                                                     |

|---------------------------|---------------|-----------------------------------------------------|

| (ada                      | lress: 0x07h) |                                                     |

| Bit                       | Term          | Description                                         |

| 0                         | ENABLE_STOP   | Enable stop function via stop switches (Default: 1) |

| 1                         | ENABLE_SLD    | Enable function of the slowdown switches            |

#### 6.3.3 STOP and SLOWDOWN-functions

The TMC453 supports stop switches (pins NSTOPL, NSTOPR) and a slowdown function (pins NSLDL, NSLDR). When an impulse occurs on the stop input which corresponds to the motor direction (increasing position value corresponds to right switch), the motor is stopped at once. This is done by setting the velocity value to zero and stopping the ramp function. The stop flag in the FIFO-Status register is set.

While an SLD input is active, the ramp generator is switched to linear ramp and the velocity is continuously decreased by the pre-programmed slowdown acceleration *fifo\_a\_sld* until the velocity *fifo\_v\_sld* is reached. The SLD function can not be used with automatic ramps. When an automatic ramp function was active, it is terminated and the motor stops at once. The application environment of the TMC453 should be designed in a way, that the SLD input stays active for at least the time that the external host processor needs to switch off the previously active ramp function, e.g. by switching to a constant ramp. Short impulses on the SLD functions could lead to uncontrolled reactions - they have to be filtered, e.g. using an RC-network. It is advised to completely control the slowdown function via software, because interaction of the processor is required in most cases. This can be efficiently realized using the interrupt ability of the SLD pins.

Stop and SLD flag are automatically reset upon read of the FIFO status register.

### 6.3.4 Finding the Reference Position

The FIFO synchronization input SYNC\_IN can be efficiently used to perform as reference input for null position finding. This is possible using the synchronization condition: The motor drives a linear or constant ramp segment in the direction of the reference switch. The next command has got the WAIT\_ON\_SYNC and the COPY\_REG\_INT bits set together with FIFO\_OVERRIDE. The reference switch then triggers this command via SYNC\_IN. The latched ramp position now describes the exact position of the reference switch.

The reference position can also be found using the stop switches and the automatic stop function: First do a rough search for the stop switch using a high velocity. Then, drive the motor out of the switch again and go back to the switch using a constant ramp with the motors start-/ stop velocity and with stop function enabled. As soon as the motor is stopped, you can set the actual position to zero.

## 6.3.5 Programming example for the FIFO

The following example shows how to program the TMC453 to start an automatic ramp in positive direction driving a 2 phase stepper motor in sine step mode. The codes for the control registers are shown in binary form (%).

- 1. Switch off the sequencer:

seq\_config Byte0 = %00000000, Byte1 = %00000000

- 2. Program sinestep and switch on the sequencer: seq config Byte0 = %10001100, Byte1 = %00000101

- 3. Program the pre-divider for the desired step frequency range, e.g. FIFO\_PRE\_DIV4 = 8 using the FIFO command SET\_RMP:

FIFO-Command Byte0 = %00001010, Byte1 = %00000111, Byte2 = 8, Byte3 = 0

- 4. Program the bow parameter, e.g.  $FIFO_BOW = 5$ :  $FIFO_Command Byte0 = %00001010$ , Byte1 = %00000110, Byte2 = 5, Byte3 = 0

- 5. Program the acceleration parameter, e.g. FIFO\_A\_NOM = 100: FIFO-Command Byte0 = %00001010, Byte1 = %00000000, Byte2 = 100, Byte3 = 0

- 6. Program the velocity parameter, e.g. FIFO\_V\_NOM = 6000 = 0x1770: FIFO-Command Byte0 = \$00001010, Byte1 = \$00000001, Byte2 = 0x70, Byte3 = 0x17

- 7. Program the target position, e.g. POS\_END = 70000 = 0x011170 using the FIFO command SET\_POS\_END: FIFO-Command Byte0 = %00001110, Byte1 = 0x70, Byte2 = 0x11, Byte3 = 0x01

- 8. Start the automatic ramp via FIFO command ARP without modification of further parameters: FIFO-Command Byte0 = %00000011, Byte1 = %00001111, Byte2 = 0, Byte3 = 0

# 7 The Ramp Generator

## 7.1 General Description

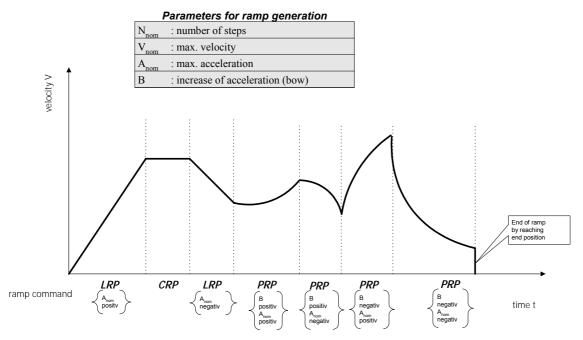

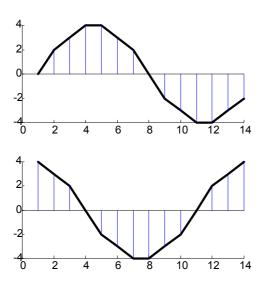

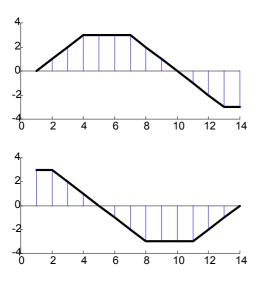

The ramp generator can generate velocity ramps (velocity over time) with constant velocity, constant acceleration and linear rising acceleration. This allows the generation of step-less and smooth ramps to avoid the motor loosing steps at the joints of each two curve segments. The so called S-curve can be generated automatically. It has got several advantages compared to the trapezoidal ramps which are commonly used for positioning tasks.

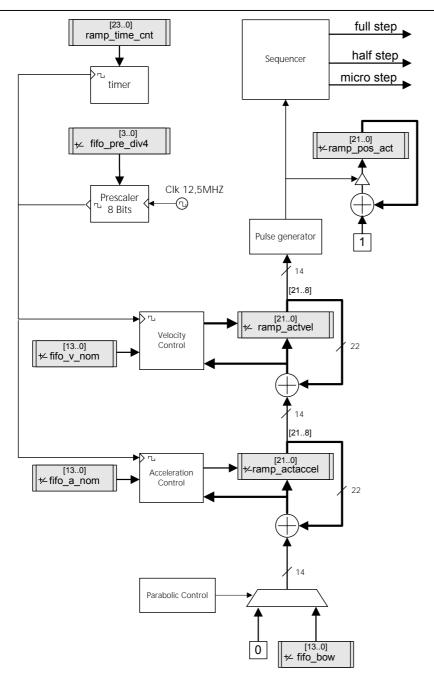

## 7.2 Principle of Operation

In principle the ramp generator is a cascade of three integrators (Figure 7-1). All integrators work with the frequency  $f_{ramp}$ , which is divided from the clock frequency via a divider ( $fifo\_pre\_div$ ) which can be programmed in powers of two. The same frequency is used to derive the step frequency of the motor. The first integrator generates a linear change of the acceleration for parabolic curves. It adds up the 14 bit wide parameter  $fifo\_bow$  in every time step to the 22 bit wide acceleration register ( $ramp\_actaccel$ ). The integrator is stopped as soon as the pre-programmed value for the nominal acceleration ( $fifo\_a\_nom$ ) is reached. The velocity value is generated using the same mechanism: The 22 bit wide velocity integrator adds up the upper 14 bits of the acceleration value in every time step until the nominal velocity ( $fifo\_v\_nom$ ) is reached.

The TMC453 avoids overflows of the integrators by stopping the integration if the next addition step would exceed the preprogrammed nominal values. Thus it is important to always choose correct nominal values to stop integration.

To yield a finer step resolution, the input values of the integrators are shifted to the right by 8 bits. This corresponds to a division by 256.

The velocity value (*ramp\_actvel*) calculated by the integrator chain feeds a programmable pulse generator, which generates one impulse for every motor step. The frequency of this pulse generator can be calculated as follows:

Step frequency of the ramp generator (Microsteps or fullsteps depending on the settings of the sequencer)

$$f_{step} = f_{clk} \cdot v/2^{14 + fifo_p re_div+1}$$

full step frequency = micro step frequency (f<sub>step</sub>) / microstep count

$f_{\text{clk}}$ : external clock frequency of the TMC453

v: actual 14 bit velocity value, signed (-8191..8191)

#### Operation frequency of the ramp generator

The calculation of the actual velocity and acceleration values as well as the time counter work with a frequency which is controlled by the pre-divider ( $f_{ramp}$ ):

$$f_{ramp} = f_{clk} / 2^{fifo\_pre\_div+1}$$

All settings of the ramp generator are controlled via the command FIFO. The corresponding registers and commands are listed in the chapter on the command FIFO.

Figure 7-1: Schematic of the ramp generator

Registers of the ramp generator

| Address | Term              | Width   | Description                                                                                                                                                                                                |

|---------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x40    | latch_ramp_params | 0 (w)   | A write access to this register causes all relevant data of the ramp generator to be copied to the ramp-holding registers.  (This is the same as the execution of a command with the bit COPY_REG_INT set) |

| 0x41    | ramp_status       | 8 (r)   | Holding register for the state of the ramp generator                                                                                                                                                       |

| 0x44    | ramp_time_cnt     | 24 (rw) | Internal ramp time reference (counts ramp generator clocks) (On read access: value of the holding register)                                                                                                |

| 0x48    | ramp_actvel       | 22 (r)  | Holding register for velocity value (s. rounding *)                                                                                                                                                        |

| 0x4C    | ramp_actaccel     | 22 (r)  | Holding register for acceleration value (s. rounding *)                                                                                                                                                    |

| 0x50    | ramp_pos_act      | 24 (r)  | Holding register for position counter (actual value)                                                                                                                                                       |

| 0x60    | fifo_a_nom        | 14 (r)  | Nominal acceleration for ramp generation                                                                                                                                                                   |

| 0x62    | fifo_v_nom        | 14 (r)  | Nominal velocity for ramp generation                                                                                                                                                                       |

| 0x64    | fifo_a_sld        | 13 (r)  | Acceleration for slowdown operation                                                                                                                                                                        |

| 0x66    | fifo_v_sld        | 13 (r)  | Final velocity for slowdown operation                                                                                                                                                                      |

| 0x68 | fifo_bow14     | 14 (r) | Ascent of acceleration (bow parameter) for ramp generation                                                            |

|------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------|

| 0x6A | fifo_a_comp1   | 13 (r) | Acceleration compare value for automatic motor current control (MC0, MC1,AOUT2)                                       |

| 0x6C | fifo_v_comp1   | 13 (r) | Velocity compare value for automatic motor current control (MC0, MC1, AOUT2)                                          |

| 0x6E | fifo_a_comp2   | 13 (r) | Acceleration compare value for automatic motor current control (MC0, MC1, AOUT2)                                      |

| 0x70 | fifo_v_comp2   | 13 (r) | Velocity compare value for automatic motor current control (MC0, MC1, AOUT2)                                          |

| 0x74 | fifo_pre_div4  | 4 (r)  | Pre-divider for ramp generator (division in powers of two)                                                            |

| 0x75 | fifo_imot0     | 8 (r)  | Output value for analog output AOUT2 for automatic ramp-dependant current control with 0 exceeded compare values      |

| 0x76 | fifo_imot1     | 8 (r)  | Output value for analog output AOUT2 for automatic ramp-dependant current control with 1 exceeded compare value       |

| 0x77 | fifo_imot2     | 8 (r)  | Output value for analog output AOUT2 for automatic ramp-dependant current control with 2 exceeded compare values      |

| 0x78 | fifo_imot3     | 8 (r)  | Output value for analog output AOUT2 for automatic ramp-dependant current control with 3 or 4 exceeded compare values |

| 0x79 | fifo_misc_ctrl | 2 (r)  | Flag for PID controller (bit 1) and flag for control based on the measured velocity (bit 0)                           |

| 0x7C | fifo_t_lim     | 24 (r) | Time limit for execution of the actual FIFO-command                                                                   |

| 0x80 | fifo_pos_end   | 24 (r) | End position for ramp segment                                                                                         |

#### (\*) Rounding of the 22 bit wide values in ramp\_actvel and ramp\_actaccel.

For all internal calculations the values in the 22 bit wide velocity and acceleration registers are rounded to 14 bit signed values. The internal rounding algorithm rounds into the direction of the next number with a higher absolute value when the least significant 8 bits have got a value between 0x80 and 0xFF for positive numbers, respectively between 0x7F and 0x00 for negative numbers.

#### Hint:

When reading the two's-complement signed numbers from the TMC453 into the host processor, please note, that they have to be sign-extended before using in 16 or 32 bit arithmetic.

| Ramp_status: 7 Bit r<br>(address: 0x41h) |                 |                                  |

|------------------------------------------|-----------------|----------------------------------|

| Bit                                      | Term            | Description                      |

| 0                                        | SLD_RIGHT       | Right slowdown switch active     |

| 1                                        | SLD_LEFT        | Left slowdown switch active      |

| 2                                        | STOP_RIGHT      | Right stop switch active         |

| 3                                        | STOP_LEFT       | Left stop switch active          |

| 4                                        | A_NOM_REACHED   | Nominal acceleration reached     |

| 5                                        | V_NOM_REACHED   | Nominal velocity reached         |

| 6                                        | POS_NOM_REACHED | Target position reached          |

| 7                                        | AUTO_ACTIVE     | Automatic ramp generation active |

## 7.3 Programming the Ramp generator

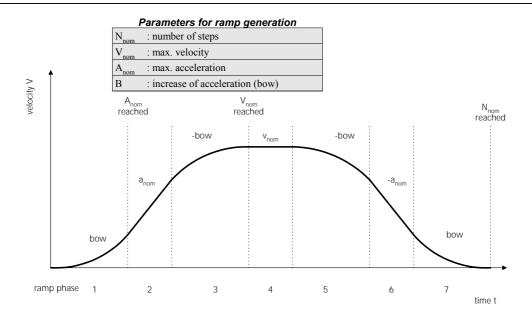

### 7.3.1 Automatic Ramp generation

Before starting a ramp, the necessary parameters of the ramp generator have to be programmed. For an automatic ramp (Figure 7-2) for example, the parameters *fifo\_bow*, *fifo\_a\_nom*, *fifo\_v\_nom*, and the target position *fifo\_pos\_end* have to be programmed. It is very important to select the signs of all parameters correctly: For example consider the motor driving in negative direction (decreasing position) – then all ramp parameters have to be set to negative values. Further the automatic ramp generator does not start if the actual velocity is different from zero.

Figure 7-2: Automatically generated S-ramp

#### Note: Terminating an automatic ramp

Should a mistake occur when programming the automatic ramp, e.g. the programmed velocity value is zero, it can only be terminated by writing a FIFO-command with the override-bit set (FIFO\_OVERRIDE) which sets the actual position to the preprogrammed target position, or by activating one of the other ramp types. In every case termination of the automatic ramp clears the values for actual velocity and actual acceleration to zero leading to an abrupt stop of the motor.

To terminate an automatic ramp and slow down to zero in a controlled way, use the following programming sequence:

- 1. Write a command for a linear ramp (LRP) into the FIFO. (This command is not yet executed!)

- 2. Program an acceleration for slowing down to zero using a write to ACTACCEL command (mind the sign!).

- 3. Set the new nominal velocity (that is 0) using a write to FIFO\_V\_NOM command.

- 4. Now read the actual velocity and, (if it is not 0 anyway,) at once write it back to the actual velocity with the override bit (FIFO\_OVERRIDE) set using a linear ramp command (LRP) combined with write to ACTVEL.

- 5. Program an acceleration of zero using a write to ACTACCEL command, to signal the automatic current control, that current can be reduced to standstill value after motor stop.

Now the TMC453 slows down to zero with the programmed acceleration. The command FIFO is empty as soon as the motor has stopped.

## 7.3.2 Programmed / Interactive Ramp generation

A number of applications requires the precise calculation of ramps, to reach certain coordinates on given points of time. An example is a plotter, where two axes have to be synchronized. In these cases the host CPU can program user defined ramps by constructing the desired curve shapes from bits of parabolic and linear ramps. Then it will be necessary to exactly control the number of steps driven in every ramp segment and to reprogram the ramp generator at the calculated positions before the next motor step is done. Because of the limited time between each two steps the TMC453 supports a programming method capable of real time reprogramming using its command FIFO: As soon as a preprogrammed condition is satisfied, the next command is fetched from the FIFO and executed. Some of the possible conditions are: Nominal velocity or nominal acceleration reached, position reached or time limit reached. To inform the host CPU, when the next command starts, it can issue an interrupt after each command. Further on a snapshot of all ramp registers can be triggered at the same moment.

Figure 7-3: User defined ramp

#### 7.3.3 Synchronization of multiple TMC453s

The command FIFO allows the synchronization of multiple TMC453s on a ramp segment basis, e.g. to start all motors in the same moment. In a typical application the host processor would program all TMC453s with the necessary commands and then start execution of the commands via the synchronization inputs (SYNCIN). Each FIFO command can specify the polarity of the SYNCIN pin as pre-condition for its execution. To start the TMC453s without further interaction of the host processor, each command can also control the polarity of the SYNCOUT pin of the TMC453. Using an external AND-operation between all SYNCOUT pins to control all SYNCIN pins in a system, allows functions like all axes waiting for the slowest one, before the next ramp is started. A step wise synchronization can be achieved by clocking multiple TMC453s with the same clock or by interconnecting the STEP\_IN and STEP\_OUT pins in the desired way.

#### Example for the programming of a ramp and FIFO usage:

| No. | No. of entries | Command                                                     |

|-----|----------------|-------------------------------------------------------------|

| 1.  | 0              | set <i>fifo_a_nom</i> (positive)                            |

| 2.  | 0              | set <i>fifo_bow</i> (positive)                              |

|     |                |                                                             |

| 3.  | 0              | set <i>fifo_v_nom</i>                                       |

| 4.  | 0              | set <i>fifo_pos_end</i>                                     |

| 5.  | 1              | start parabolic curve with SYNCIN condition                 |

| 6.  | 2              | set <i>fifo_bow</i> again (negative), Start linear movement |

| 7.  | 3              | set <i>fifo_a_nom</i> to 0, start parabolic curve           |

| 8.  | 4              | set <i>fifo_a_nom</i> (negative), start constant phase      |

|     |                |                                                             |

Now set sync signal to start execution.

This example shows the programming of the first half of an S-curve.

## 7.4 Ramp adaptive motor current control

In many applications the stepper motor drives dynamic loads. Dynamic loads require a low static torque but a high torque when accelerating. To meet all requirements, the TMC453 is equipped with two compare registers for velocity control and two compare registers for acceleration control (fifo\_a\_comp1/2, fifo\_v\_comp1/2). The sum of the values exceeded in each moment is available as binary number at the outputs MC0/MC1 (limited to 0 to 3). At the same time this sum is used as a pointer to one of four IMOT registers. The value of the selected IMOT-Registers can be output to DAC2. This DAC can be used for control of the motor current by using the DAC2 output voltage as reference voltage for DAC0 and DAC1 in microstepping applications. A time dependant current control can be achieved using the timer commands of the command FIFO.

## 8 The Incremental Encoder Interface

## 8.1 General Description

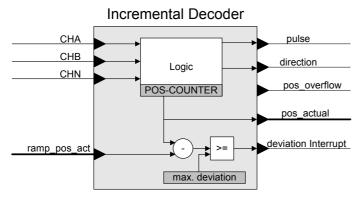

This module decodes the signals of a digital incremental encoder (CHA,CHB,CHN) and provides a position register. Additional function registers allow position comparison of ramp position (ramp generator) and actual position (encoder) to monitor the stepper motor, or to enable regulation via the integrated PID controller. An interrupt can be issued when the difference exceeds a user programmable maximum value. Further the encoder signals can be converted to pulse and direction signals.

Figure 8-1: Schematic of the Incremental Encoder Interface

## 8.2 Registers of the Incremental Encoder Interface

| enc_control: 7 bit rw<br>(address: 0x10h) |                      |                                                                                 |  |

|-------------------------------------------|----------------------|---------------------------------------------------------------------------------|--|

| Bit                                       | Bit Term Description |                                                                                 |  |

| 0                                         | CHN_POL              | Selects the polarity of the CHN input. [1]: positive, [0]: negative             |  |

| 1                                         | CLR_POS_CNT_CHN      | Set: The next CHN signal sets <i>ENC_COUNT</i> to zero                          |  |

| 2                                         | LTH_POS_CNT_CHN      | Set: The next CHN signal copies <b>ENC_COUNT</b> to <b>LTH_POS</b>              |  |

| 3                                         | LTH_POS_CNT_IMD      | ENC_COUNT is copied to LTH_POS at once (bit resets automatically)               |  |

| 4                                         | ACT_POS_IS_NOM_POS   | ENC_COUNT is loaded with the ramp position RAMP_POS_ACT at once (bit resets     |  |

|                                           |                      | automatically)                                                                  |  |

| 5                                         | LTH_POS_CNT_RAMP_PAR | ENC_COUNT will be copied to LTH_POS together with the ramp parameters (when bit |  |

|                                           |                      | COPY_REG_INT is set in a FIFO command).                                         |  |

| 6                                         | DIR_POL              | Defines the direction of the encoder signals. [1]: CHA->CHB, [0]: CHB->CHA      |  |

| enc_portstat: 3 bit r<br>(address: 0x11h) |      |                             |

|-------------------------------------------|------|-----------------------------|

| Bit                                       | Term | Description                 |

| 0                                         | CHN  | State of the input port CHN |

| 1                                         | СНВ  | State of the input port CHB |

| 2                                         | CHA  | State of the input port CHA |

| enc_count: 24 bit rw<br>(address: 0x14h) |           |                                     |

|------------------------------------------|-----------|-------------------------------------|

| Bit                                      | Term      | Description                         |

| 0-                                       | ENC_COUNT | Actual value of the encoder counter |

| 23                                       |           |                                     |

| enc_holdreg: 24 bit r<br>(address: 0x18h) |         |                                                       |

|-------------------------------------------|---------|-------------------------------------------------------|

| Bit                                       | Term    | Description                                           |

| 0-                                        | LTH_POS | Holding register for encoder counter <b>ENC_COUNT</b> |

| 23                                        |         |                                                       |

| enc_prediv_cnt: 8 bit rw<br>(address: 0x1Ch) |                 |                                                                     |

|----------------------------------------------|-----------------|---------------------------------------------------------------------|

| Bit                                          | Term            | Description                                                         |

| 0-                                           | ENC_PRE_DIV_CNT | Pre-divider for incremental encoder (counts encoder signal changes) |

| 7                                            |                 |                                                                     |

|   |    | prediv_ratio: 8 bit rw<br>ress: 0x1Dh) |                                                                      |

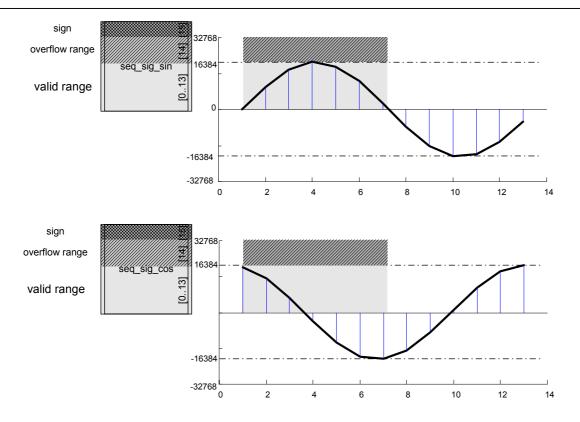

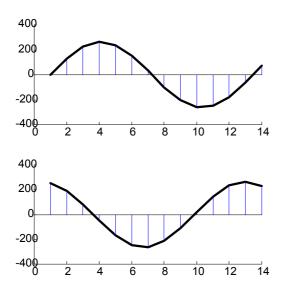

|---|----|----------------------------------------|----------------------------------------------------------------------|